|

NoSync by g0blinish

[nfo]

|

||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

|

|||||||||||||

|

popularity : 51% |

|||||||||||||

alltime top: #39951 |

|

|||||||||||||

|

||||||||||||||

| added on the 2017-12-11 14:07:57 by g0blinish |

||||||||||||||

popularity helper

comments

not very interesting, but a compofiller so.. motivational piggie perhaps?

added on the 2017-12-11 16:04:59 by Tjoppen

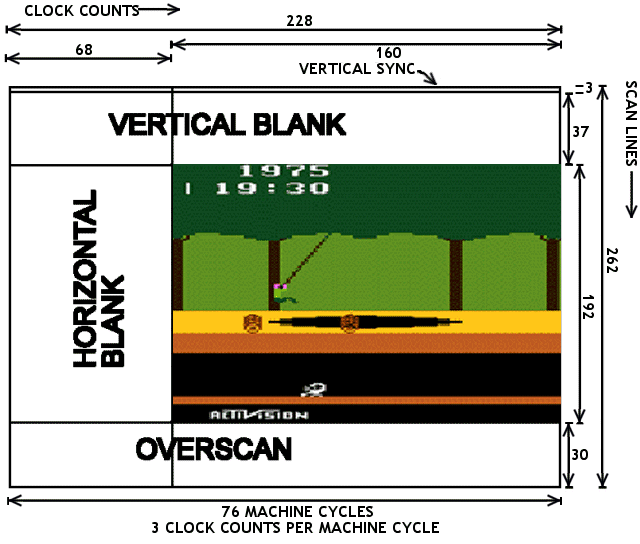

Not sure what sync you're talking about, but as for the "broken lines", it's because you sta COLUBK during the horizontal draw. You should do it during horizontal blank: in pt, do sta WSYNC just before sta COLUBK, and remove the sta WSYNC under, before the bne Loop1. I doubt your loop body takes exactly 68 cycles each line, with so many cmp / bxx. You can see in Stella exactly where is the beam when you step over each instruction.

Every A2600 release deserves a thumb ;) And all the best for the next steps on A2600! You are so multi-skilled g0blinish. Respect.

hey g0blinish, little explanation for your question. what you see up your schema are TIA cycles. you have 228 of them per line, TIA clock is counting pixels. the 68 means that for each line you have 68 pixels drawn on left of the screen that you will never see, and 160 that you will see on the screen, so total is 228. the real CPU cycles are down the schema "76 machine cycles" per line. and as explained, it is 3 TIA clock counts for 1 machine cycle. This means that when 1 CPU cycle elapses, the TIA outputs 3 pixels during the same time. 228 TIA clocks / 3 = 76 CPU cycles. So if you want to change color cleanly, you have to do it in the first 68 / 3 = 23 CPU cycles of the line. if you do it after it will be seen on the screen. Good luck :)

:P

Doing anything on the VCS is a challenge, so piggie

VCS majik...

submit changes

if this prod is a fake, some info is false or the download link is broken,

do not post about it in the comments, it will get lost.

instead, click here !